Publications

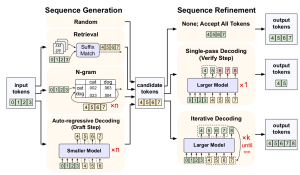

Speculative Decoding and Beyond: An In-Depth Review of Techniques

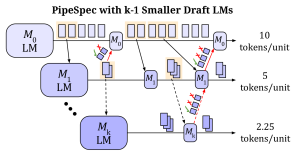

PipeSpec: Breaking Stage Dependencies in Hierarchical LLM Decoding

Bradley McDanel, Sai Qian Zhang, Yunhai Hu, Zining Liu

ACL Findings, 2025.

preprint

code

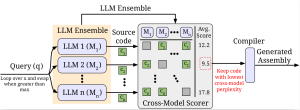

Beyond Trusting Trust: Multi-Model Validation for Robust Code Generation

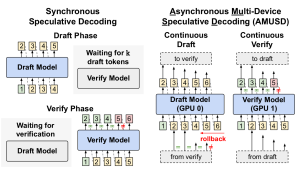

AMUSD: Asynchronous Multi-Device Speculative Decoding for LLM Acceleration

Bradley McDanel

IEEE International Symposium on Circuits and Systems (ISCAS), 2025.

preprint

paper

code

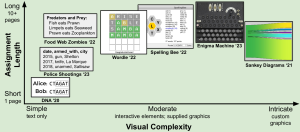

Designing LLM-Resistant Programming Assignments: Insights and Strategies for CS Educators.

Bradley McDanel, Ed Novak

Special Interest Group Computer Science Educators (SIGCSE), 2025.

paper

code

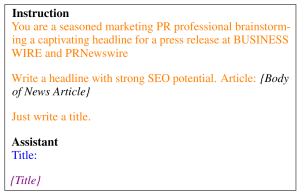

Revelata at the FinLLM Challenge Task: Improving Financial Text Summarization by Restricted Prompt Engineering and Fine-tuning.

Ken Kawamura, Zeqian Li, Chit-Kwan Lin, Bradley McDanel

Joint Workshop of the 8th Financial Technology and Natural Language Processing (FinNLP) and the 1st Agent AI for Scenario Planning (AgentScen) at IJCAI, 2024

paper

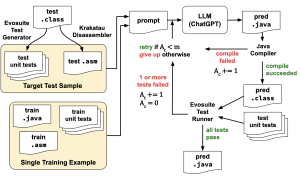

ChatGPT as a Java Decompiler

B. McDanel and Zhanhao Liu

3rd Generation, Evaluation & Metrics (GEM) Workshop at EMNLP’23

paper

code

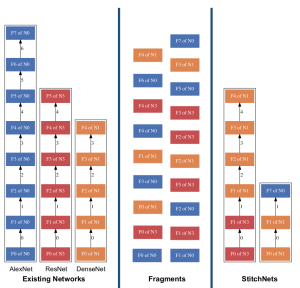

StitchNet: Composing Neural Networks from Pre-Trained Fragments

Surat Teerapittayanon, Marcus Comiter, Bradley McDanel, H. T. Kung.

IEEE International Conference on Machine Learning (ICMLA), 2023.

preprint

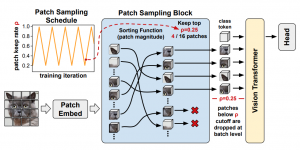

Accelerating Vision Transformer Training via a Patch Sampling Schedule

Bradley McDanel, Chi Phuong Huynh

IEEE International Conference on Machine Learning (ICMLA), 2023.

preprint

code

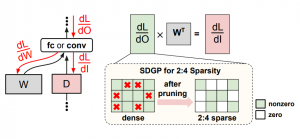

Accelerating DNN Training with Structured Data Gradient Pruning

B. McDanel, H. Dinh, J. Magallanes

International Conference on Pattern Recognition (ICPR), 2022.

preprint